# Chiplet 封装设计中信号 完整性仿真挑战及应对

精准仿真，赋能未来

# 目录

01

Chiplet 封装的主要形式

02

Chiplet 封装设计中涉及仿真的挑战及应对

03

巨霖高精度高速信号完整性解决方案

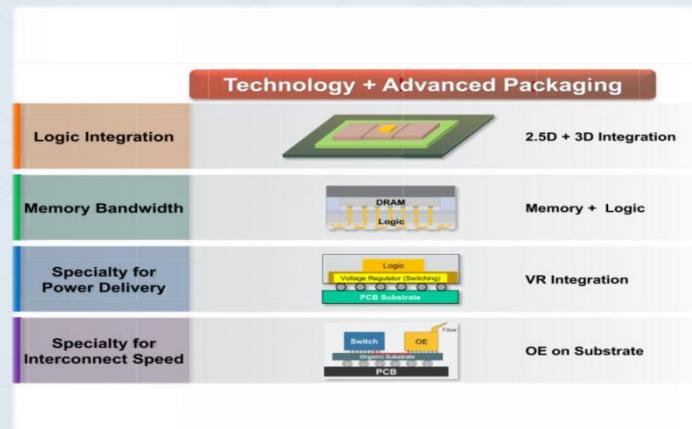

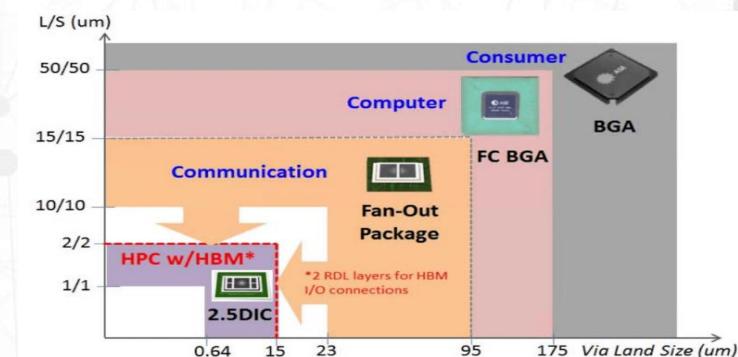

# Chiplet 封装类型及应用

| Package Type    | 2D   | 2.1D   | 2.3D   | 2.5D | 3D   |

|-----------------|------|--------|--------|------|------|

| Schematic Image |      |        |        |      |      |

| L/S (μm)        | 9/12 | ~2/2   | ~2/2   | <1/1 | <1/1 |

| I/O Density     | Low  | Middle | Middle | High | High |

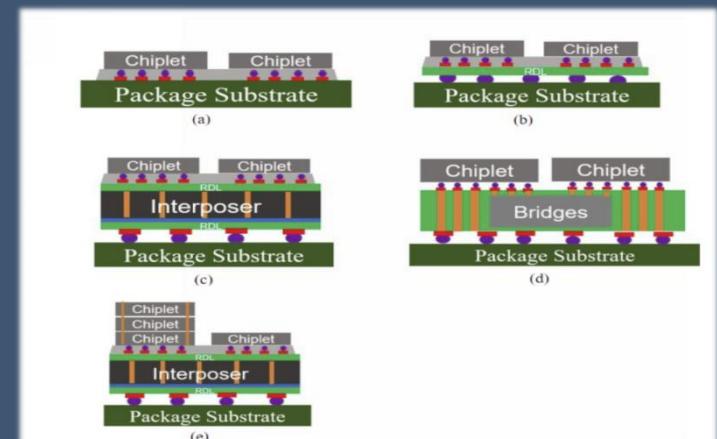

Chiplet 封装典型应用

2.3D/2.5D 以及与 3D 的

混合是目前主流类型 b/c/d/e

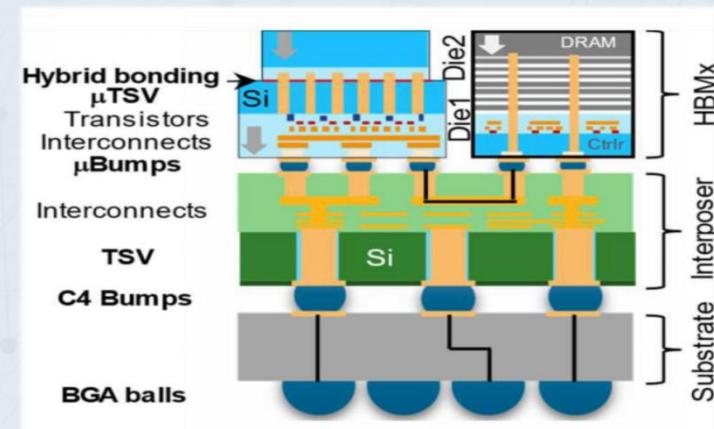

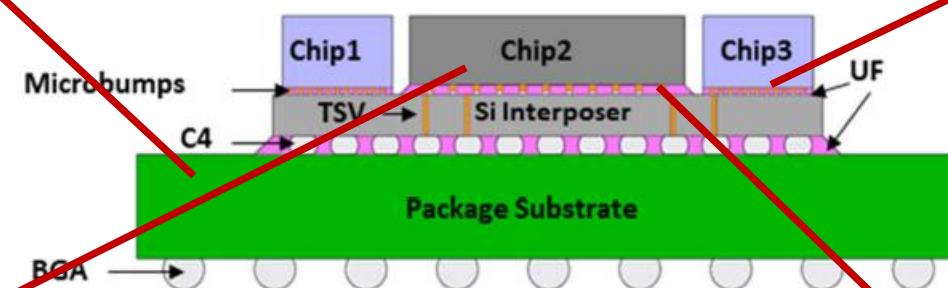

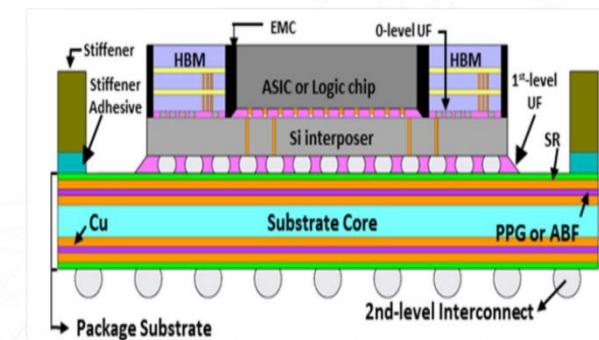

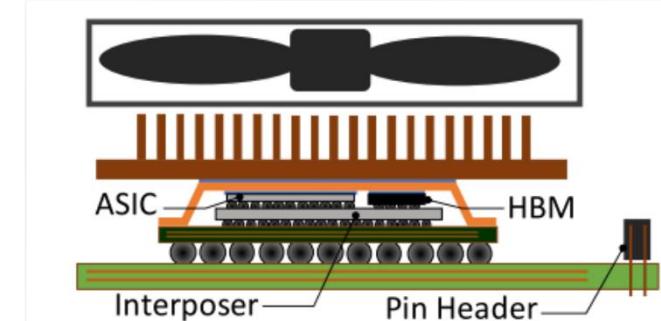

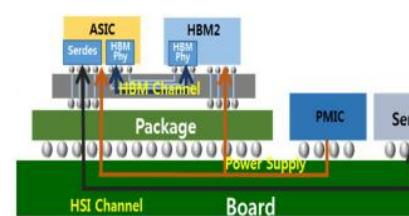

## 2.5D+3D Chiplet 封装结构

# 目录

01

Chiplet 封装的主要形式

02

Chiplet 封装设计中涉及仿真的挑战及应对

03

巨霖高精度高速信号完整性解决方案

# Chiplet 封装设计中涉及仿真的主要问题

机械-翘曲

信号完整性

电源完整性

功耗-散热

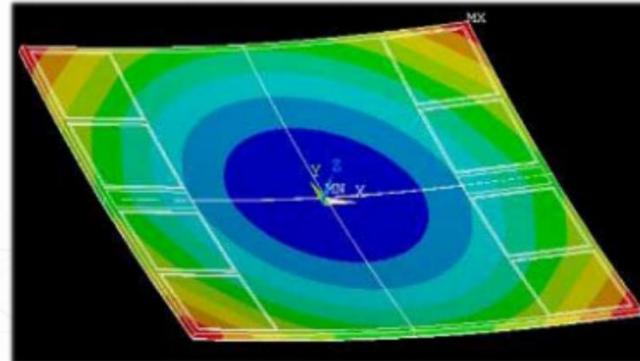

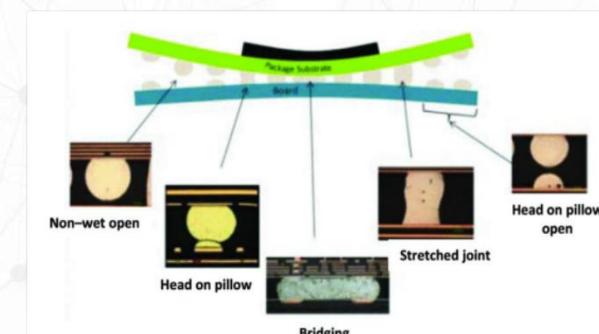

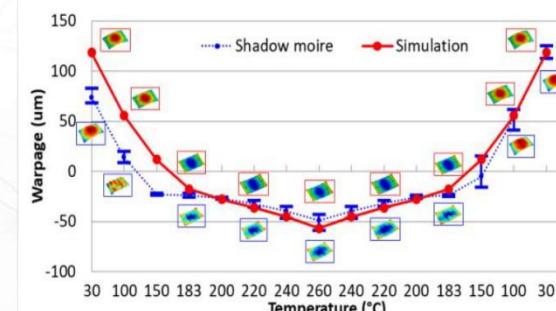

# Chiplet 封装设计中的机械-翘曲问题

## Chiplet 封装中机械-翘曲问题更加突出：

- 封装/扇出区域尺寸一般较大

- 材料种类更多，接口、结构更加复杂

- 功耗高，热效应导致的应力更大

- 造成的代价更大

## 机械-翘曲问题仿真难点：

- 与生产过程、处理流程相关性大，Fabless 较难全面、准确模拟

- 实际使用的材料属性与仿真的材料属性可能有偏差

- Etc.

## 可能的解决方案：

- 与成功案例作对比机械-翘曲仿真

- OSAT 提供解决方案建议及实际 DOE 建议

- 仿真与实际 DOE 结果作拟合，积累经验

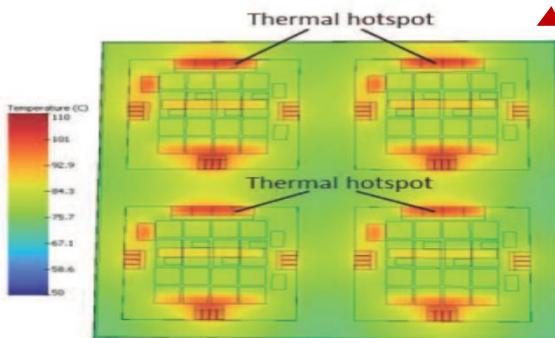

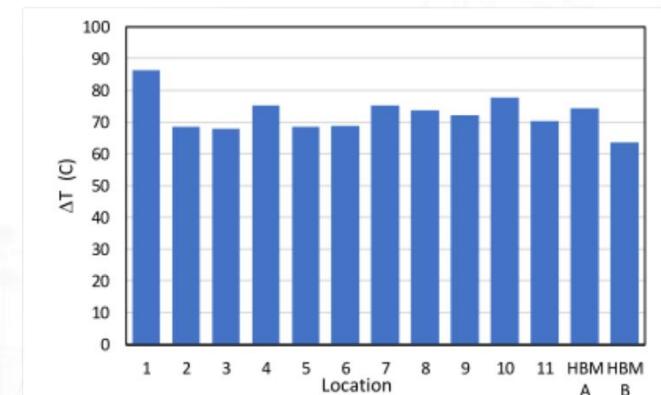

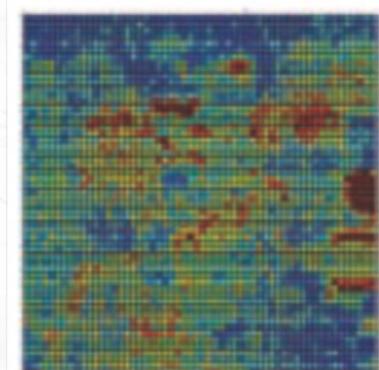

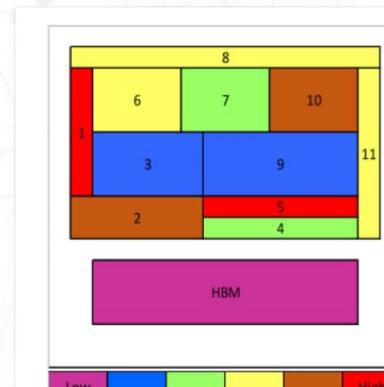

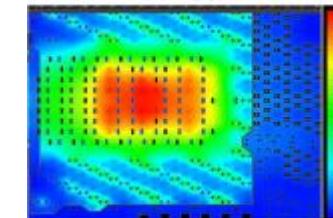

# Chiplet 封装设计中的功耗-散热问题

## Chiplet 封装中功耗-散热问题：

- 集成度高，芯片性能高，整体功耗高，温度梯度高

- 多芯片集成，功耗场景更加复杂

- D2D 高带宽互连功耗密度大，而对可靠性要求高

## Chiplet 封装中功耗-散热问题仿真难点：

- 最差功耗场景不易确定

- 大芯片功耗密度差异较大，功耗需精确至 Die 内模块级

- 模型剖分精度需要精确至 Die 模块级别

## 可能的解决方案：

- 与后端、综合部门合作，获取关键模块的场景功耗

- 与系统部门合作，获取系统不同场景的功耗分布

- 仿真工具能识别 Die-封装-PCB-系统结构件，从而能自适应的进行网格剖分，平衡精度与效率

- 热测试与热仿真迭代修正

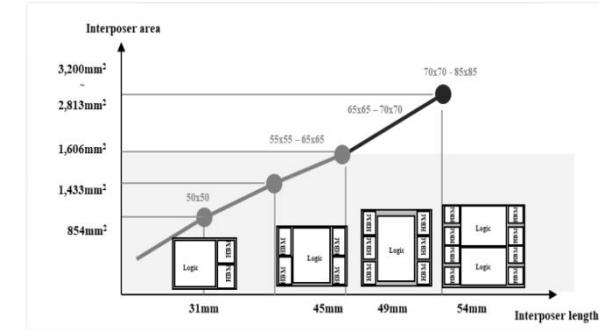

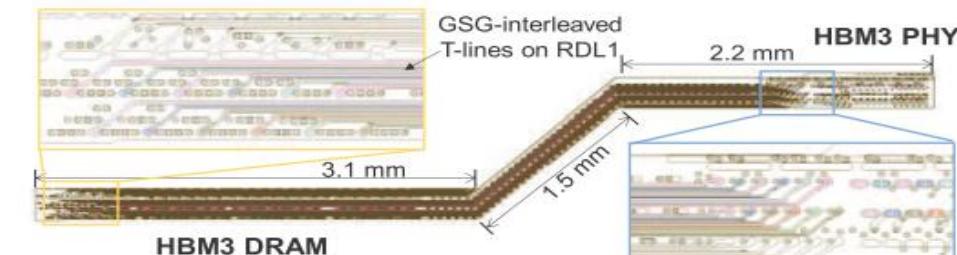

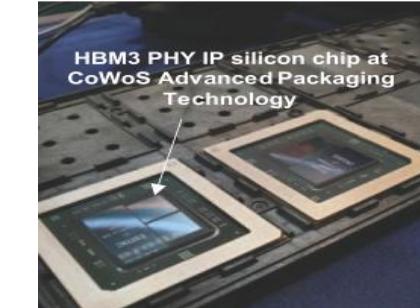

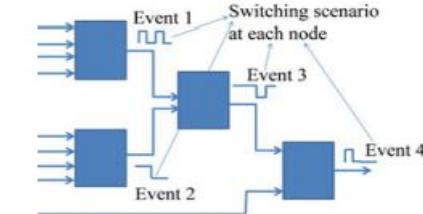

# Chiplet 封装设计中的信号完整性挑战

## Chiplet 封装中信号完整性挑战：

- 封装集成度高，信号布线密度高，串扰大。

- D2D 接口信号速率高，并行接口如 HBM3E 达 9.2Gbps, UCIE 高达 32Gbps, XSR Serdes 接口可达 112 Gbps。

- D2D 接口对功耗要求高，IO 设计尽可能简化从而无法兼顾太多 SI 性能。

## Chiplet 封装中信号完整性问题仿真难点：

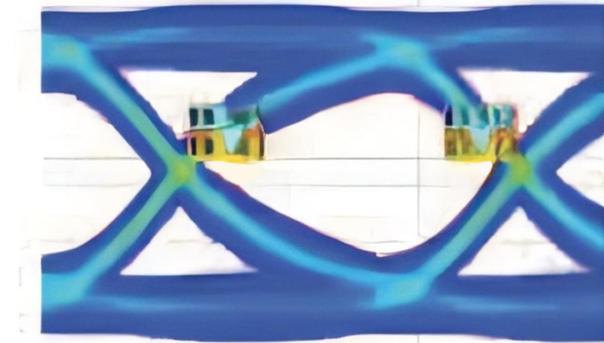

- EM 建模难度高，尺寸精度从亚 um (RDL/interposer) 到 10um(substrate) 到几十 um(PCB) 级别,网格剖分难度高。

- 系统 Timing 裕量低。

## 可能的解决方案：

- EM 仿真工具能识别 Die-封装-PCB-系统结构件，从而能自适应的进行网格剖分。

- SI/PI 协同做 SPICE 级别的精确电路仿真。

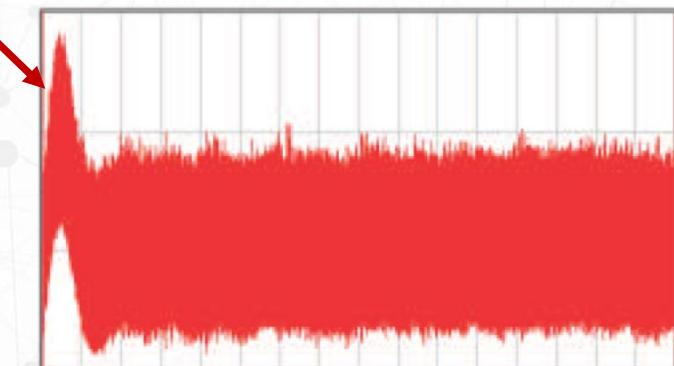

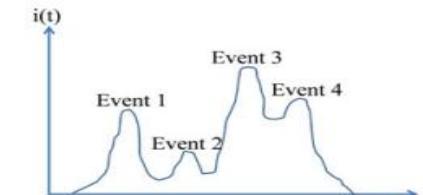

# Chiplet 封装设计中的电源完整性挑战

## Chiplet 封装中电源完整性挑战：

- AI/HPC 芯片中 Core 电源电流大，频率高。

- AI 应用中计算场景可能产生固定频率的功耗，对电源网络设计构成挑战。

- 高速接口速率高，电源电流大且对电源噪声要求高。

## Chiplet 封装中电源完整性问题仿真难点：

- EM 建模难度高，尺寸精度从亚 um (RDL/interposer) 到 10um(substrate) 到几十 um(PCB) 级别,网格剖分难度高； Hybrid solver 无法在 interposer 上保证精度。

- Core 电源需要典型噪声场景电流。

- IO 电源需要与信号完整性一起，仿真最差 SI/PI 场景噪声。

## 可能的解决方案：

- EM 仿真工具能识别 Die-封装-PCB-系统结构件，从而能自适应的进行网格剖分。

- DC / 瞬态噪声都要通过仿真优化至满足设计 SPEC。

- 对于 IO 接口电源，设计触发最坏噪声及 SSN 的码型，SI/PI 协同做 SPICE 级别的精确电路仿真。

# Chiplet 封装仿真挑战总结

## ■ 机械-翘曲

- Chiplet 封装由于尺寸大，结构复杂、材料种类多，翘曲问题尤其严重。

- 仿真通常无法精确模拟生产过程、工艺流程、所用的材料参数。

- 通常由 OSAT DOE 并由 Fabless 仿真逐步寻求最优方案。

## ■ 功耗-热

- Chiplet 封装内的芯片一般功耗高、功耗密度大、温度梯度高、场景复杂。

- 建模需要综合考虑芯片-封装-PCB-系统结构级尺寸，网格剖分难度大。

- 需要仿真、测试不断迭代，找到最差场景，积累设计经验。

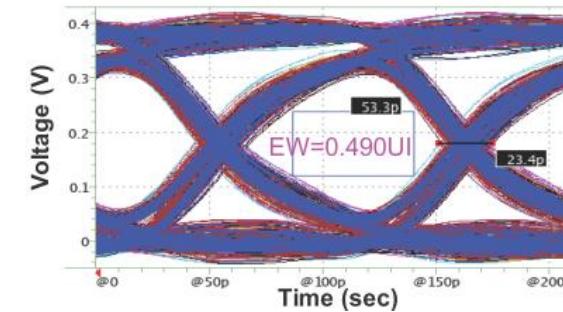

## ■ 信号完整性

- Chiplet 封装内的信号，尤其是 D2D 接口，信号速率较高，布线密度大，IO 设计简单，保持信号裕量的挑战很大。

- 传统的EM建模一般是针对 10um 级别的设计，而 Chiplet 封装是亚 um 级别的布线，这是对 EM 工具的挑战。

- 时域仿真上，由于 Chiplet 封装系统 Timing 裕量紧张，需要 EDA 工具支持 SI/PI 协同做 SPICE 级别的精确电路仿真从而保证设计 sign-off。

## ■ 电源完整性

- Core 电源电流大、场景复杂且频率高、IO 接口电源噪声要求高是主要设计挑战。

- EM 建模上具有信号完整性类似的难题，而在时域仿真上，同样需要高精度的 SPICE 级仿真工具确保系统级电源噪声的 sign-off。

# 目录

01

Chiplet 封装的主要形式

02

Chiplet 封装设计中涉及仿真的挑战及应对

03

巨霖高精度高速信号完整性解决方案

# 高精度高速信号完整性仿真关键技术

## 高保真电路模型

- **SPICE 模型**: 高频信号中的非线性效应导致建模复杂，需要高保真的 SPICE 模型进行电路仿真，以精确模拟各种元件的非线性特性。

- **S 参数模型**: 需要用 S 参数精确描述复杂网络的传输和反射特性。

## 高精度电路级与统计仿真求解

- **电路级仿真**: 需要精确的时域仿真求解器，对 S 参数进行处理（阶跃响应等）；利用 TDR 技术分析信号反射特性，识别阻抗不匹配。

- **统计仿真**: 需要高精度的统计眼图算法，进行 SerDes 链路信号完整性仿真，分析链路 BER 性能。

## 高精度的电磁场模拟

- **S 参数提取**: 高精度的 S 参数模型来源于高精度的电磁场求解，关键技术包括 (msh 算法，AMR，matrix slover 等)。

- **EMI**: 使用有限元法 (FEM) 或边界元法 (BEM) 进行 EMI 分析。

# 巨霖科技提供高速信号完整性一站式解决方案

**EMArtist**

业界先进的

SI/PI/EMI/EMC 仿真工具

**SIDesigner**

True-Spice 级别精度的高

速信号完整性仿真工具

打造从芯片-封装-系统的一站式信号完整性解决方案

**EM SOLVER**

FEM/FDTD/MOM 等混合电磁

场求解、域分解、HPC 技术

**TJSPICE/TJSPICE-RF**

对标 HSPICE 的高品质

电路仿真引擎

# 基于高精度电路仿真根技术，缔造下一代 SI 仿真签核标准

## 面向未来的超高速信号完整性解决方案

HSPXXX 是标杆客户传统的 SI 瞬态仿真精度标准，但在统计眼图方面不够优异。

SI 1.0

Golden

SPICE

SI 2.0

业内同类

SI 平台

SI 3.0

(面向 AI&HPC 时代)

TJSPICE&SIDesigner

历经标杆客户业务部门近四年的打磨及大批量使用，通过大量案例证明，TJSPICE&SIDesigner 不仅完美解决了传统的高精度 SI 瞬态仿真问题，并针对上述 2.0 时代无法克服的挑战，助力面向未来的高性能芯片仿真设计。

统计眼图功能完备，但无法达到 True-SPICE 级别精度，信号频率高到一定程度之后，现有仪器设备无法测量出高速信号的眼图，从而使得 2.0 时代无法解决日益迫切的高精度高速信号统计眼图仿真挑战。

# 基于高精度电路仿真根技术-巨霖 SIDesigner 平台

## 功能优势

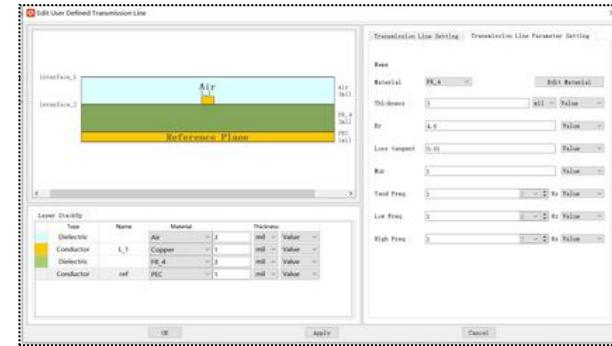

### 传输线自由建模：精准+快速

- 精准：覆盖十余种材料，及定义其电磁性质

- 快速：操作便捷

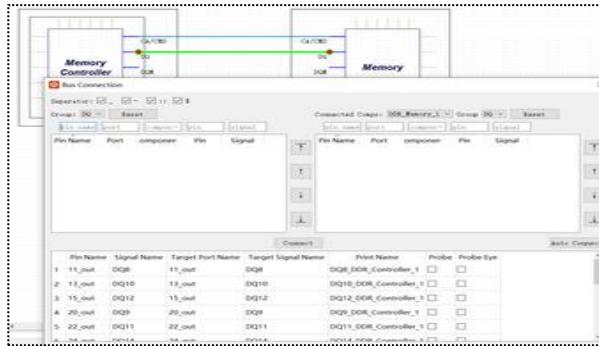

### DDR Component: 精准+高效

- 精准：经客户案例验证，较 3<sup>rd</sup> Party Spice 误差 0.2%

- 高效：ibis 批量编辑、bus 自动连接...

### 低速 SI 后仿：精确+高效+易用

- 精确：经客户案例验证，较 3<sup>rd</sup> Party 误差 3%

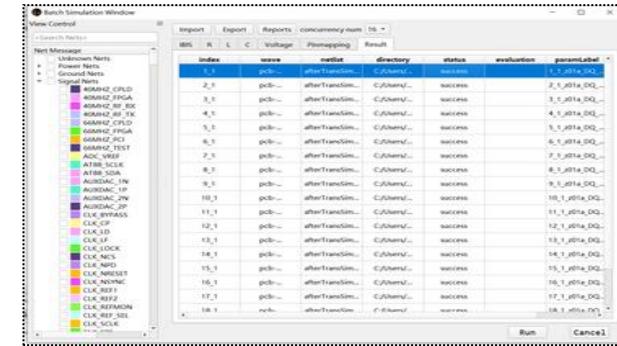

- 高效：多线并行仿真、sweep、一键生成报告...

- 易用：xlsx 批量导入

## 易用性优势

- 贴近用户使用习惯,低成本进行工具切换

- 实现波形显示设置保存和自动刷新功能

- 支持层次化原理设计和总线设计

- 输入 excel 配置表格,全自动完成批量拓扑提取,仿真,输出报告流程

- 大规模节约了工程师的时间,低速 SI 后仿效率提高 10 倍以上

# 高速信号完整性解决方案的高性能芯片仿真实例

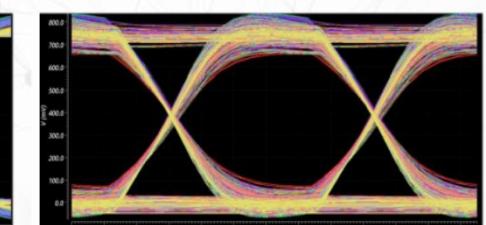

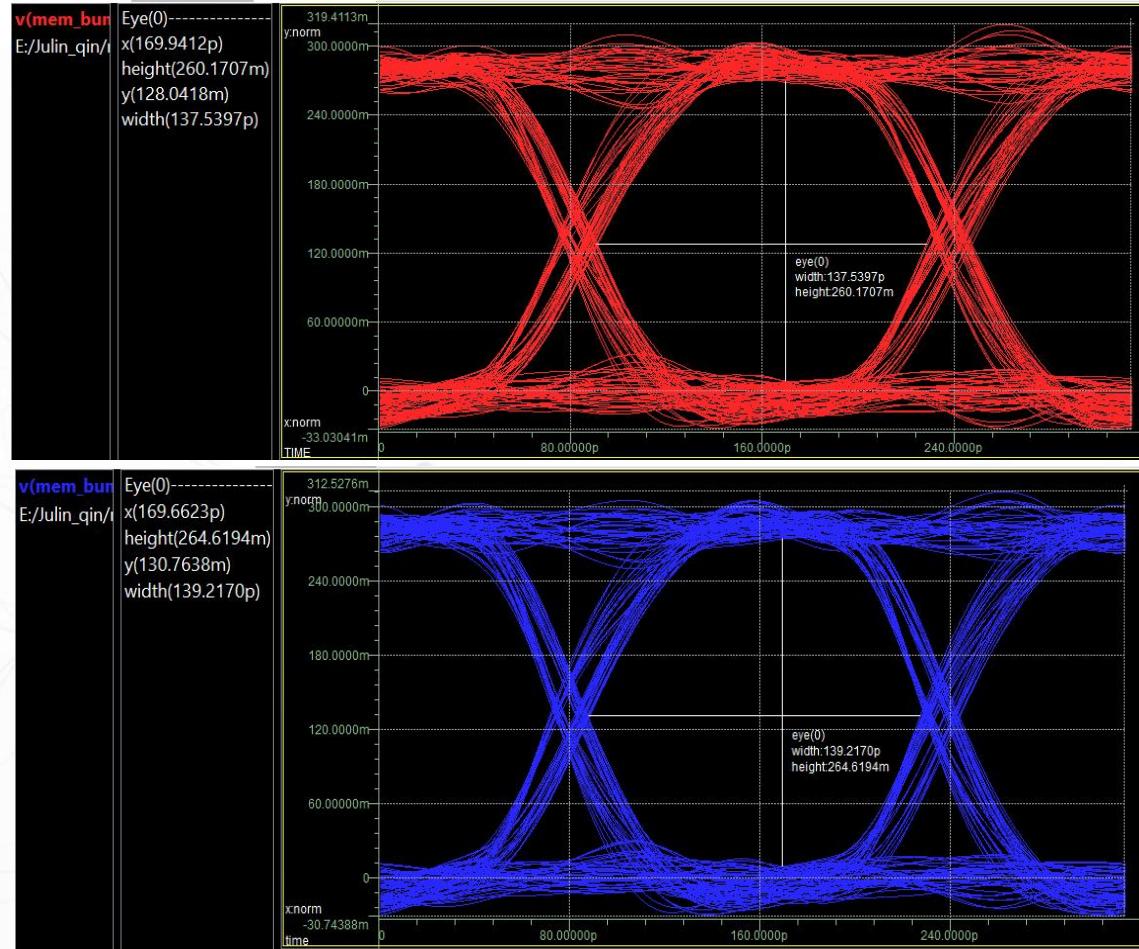

## 某 GPU 设计中 DDR4 的仿真实例

3<sup>rd</sup> Party Spice

SIDesigner

## measurements

|                             | HEIGHT         | WIDTH          |

|-----------------------------|----------------|----------------|

| 3 <sup>rd</sup> Party Spice | 260.1707m      | 137.5397p      |

| SIDesigner                  | 264.6194m      | 139.2170p      |

| <b>Delta</b>                | <b>4.4487m</b> | <b>1.6733p</b> |

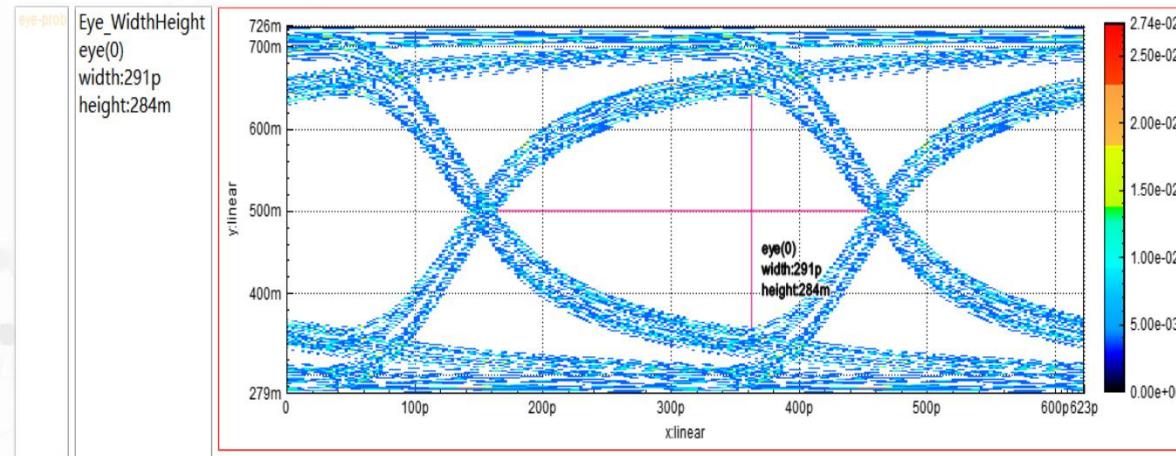

# 高速信号完整性解决方案的高性能芯片仿真实例

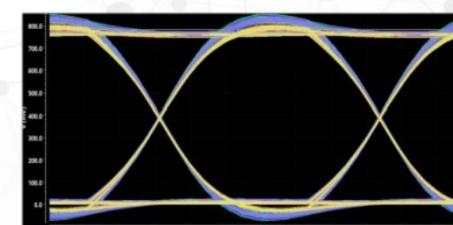

## SIDesigner

## 3<sup>rd</sup> Party

## PCIE 通道仿真对比

算法: Bit by bit: 150000

激励源: PRBS 8bit

## measurements

|                       | HEIGHT | WIDTH |

|-----------------------|--------|-------|

| 3 <sup>rd</sup> Party | 281m   | 289p  |

| SIDesigner            | 284m   | 291p  |

| ( $\Delta$ )          | 1.07%  | 0.69% |

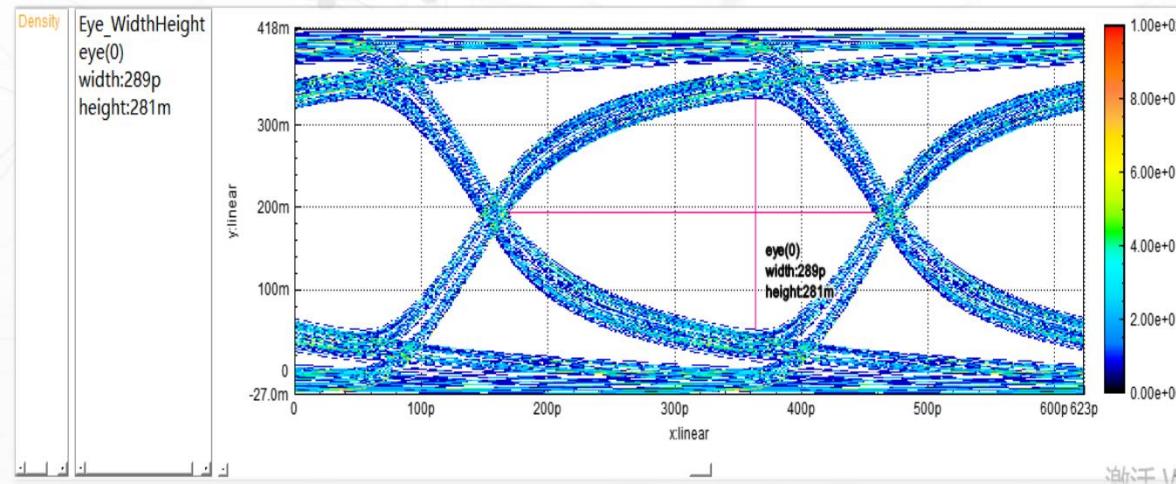

# 高速信号完整性解决方案的高性能芯片仿真实例

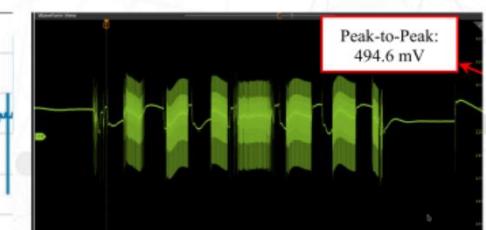

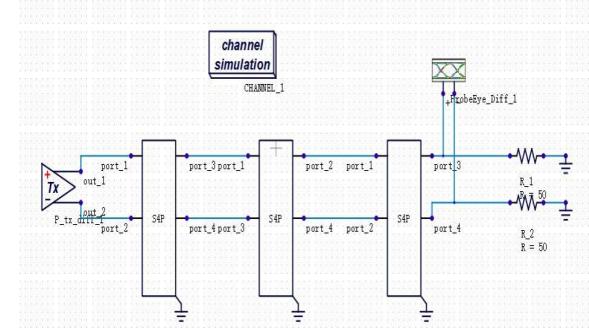

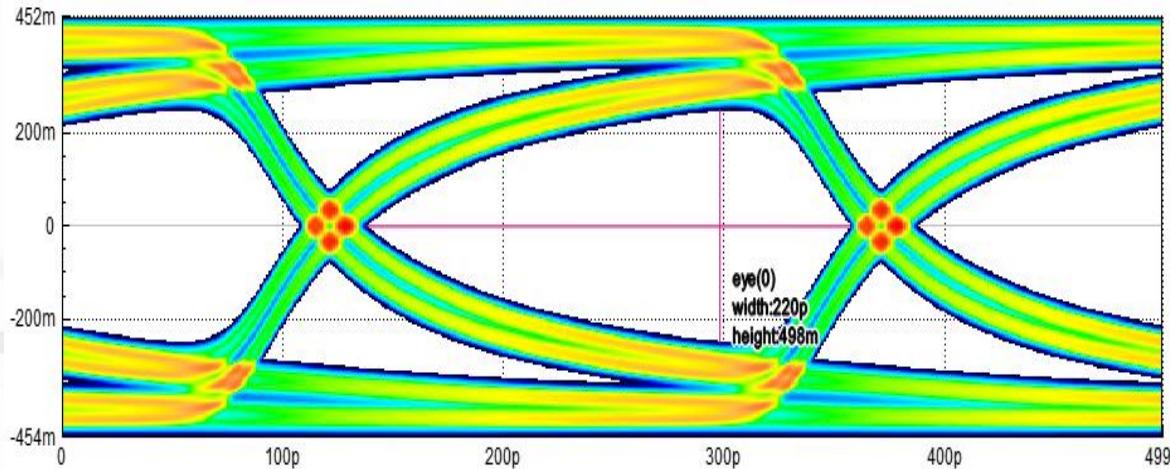

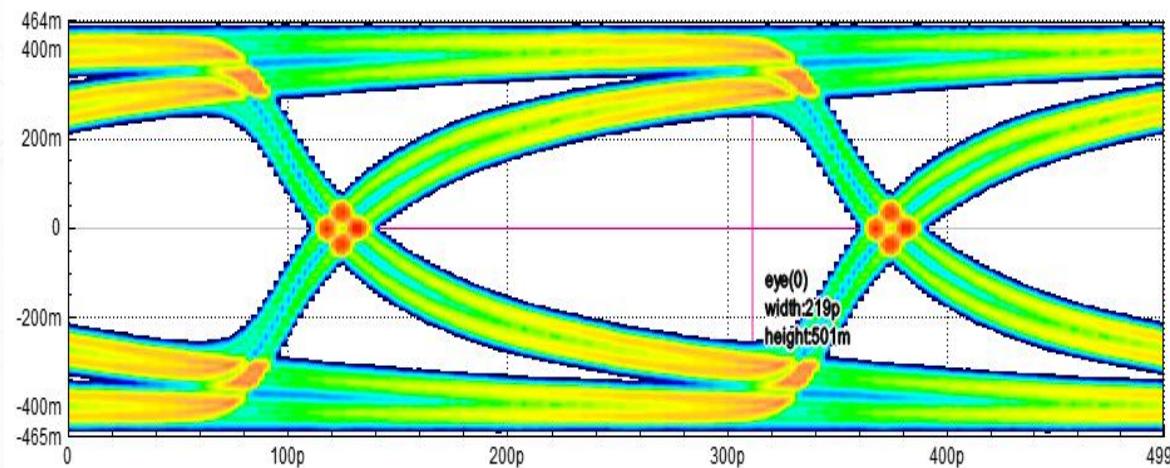

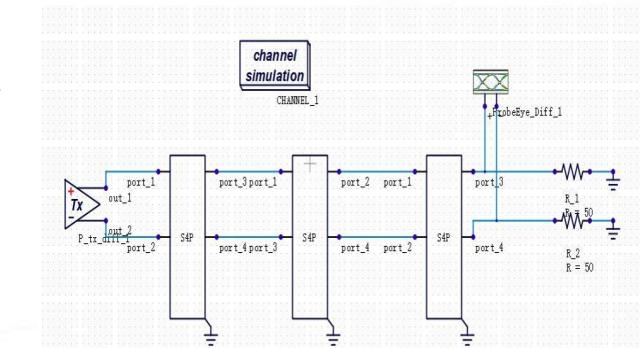

## SIDesigner

## 3<sup>rd</sup> Party

**案例说明：串行 SerDes 结构（带 DFE 均衡）**

**激励源 (PRBS) :**

freq=4Gbps

rise/fall time=3ps

vinl=-1V; vinh=1V

**通道仿真：**

Statistical Eye

measurements

|                       | HEIGHT | WIDTH |

|-----------------------|--------|-------|

| 3 <sup>rd</sup> Party | 501m   | 219p  |

| SIDesigner            | 498m   | 220p  |

| ( $\Delta$ )          | 0.6%   | 0.46% |

# 感谢观看！

精准仿真，赋能未来

扫码了解更多